Nanowire 3D Transistors Becomes More Compact

A transistor is a very important electronic device which is used to amplify and switch electronic signals. Semiconductor Chip makers started to use 3D Transistors in 2011 to reduce the size and increase the efficiency of chips. They can pack more 3D transistors into a single chip since it is much more compact than traditional planar transistor.

The amount of compactness will not be sufficient for future generations of semiconductor chips and to keep the pace of Moore’s Law. Thus there is a need to shrink these 3D transistors and one possible way to do this is by using nanowires in the transistor design. The area of nanowire based transistor is about half of the traditional planar transistor and it will be lesser if we consider more complicated components.

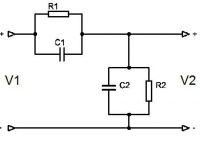

Xiang Li at the A*STAR Institute of Microelectronics and his co-workers have find a new design by integrating two transistors onto vertical silicon nanowire. This new design will reduce the areal density limit of 3D transistors even further. They have used ‘gate-all-around’ gates or wrap-around gates for making the new device. These devices having gates consists of vertical cylinder, centre of which nanowire passes through as shown in the diagram.

The new design decreased the area required for a Gate All Around transistor by a factor of 2, as they constructed two transistors by using single nanowire. As shown in the above diagram, gates are placed one above the other and are separated using a thin layer of dielectric to isolate them electrically. Unlike other independent double gate transistor designs, the change in voltage on one transistor will not affect the threshold (turn on) voltage of other transistor. Thus either of the gate can control the nanowire current independently.

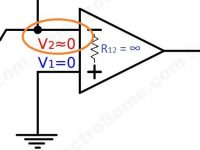

As a result, Xiang Li and his co-workers was able to create a simple logic device by using just one nanowire. If the nanowire is doped with negative carriers, then the current will be able to flow through nanowire when both gate voltages are high. If either of them is low, it will not conduct. Thus this device can function as AND gate, which requires only about half area that it would usually needs.

The design used here can also be used in Tunnelling Field Effect Transistor (TFET). Since it have great applications, as they turn on very quickly and very low power consumption. Li said that, that the tunnelling junction of TFET should made using two gates similar to dual gate nanowire geometry. Like this, there are many other possible applications.